#ldmx

# **Backplane-less readout for HGCROC board quality control**

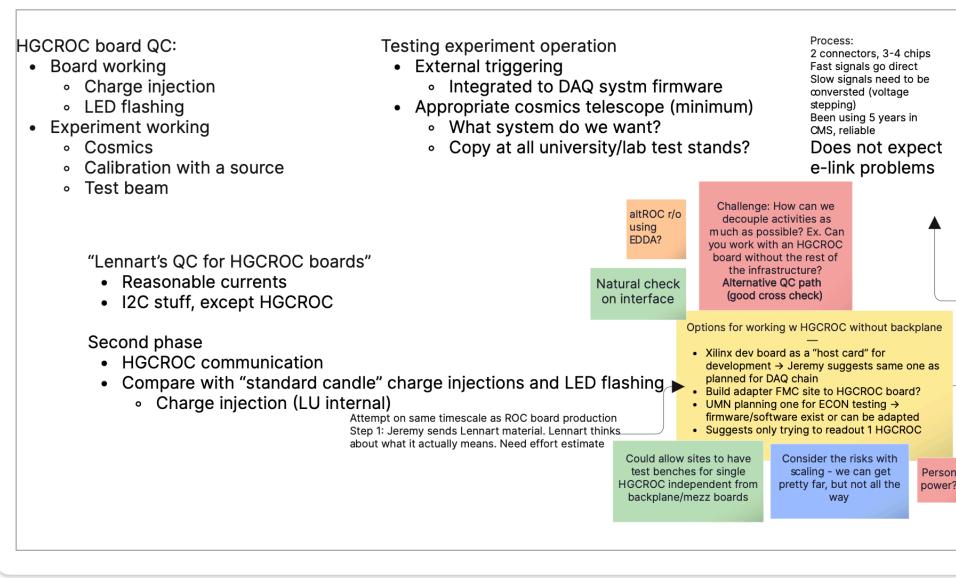

What should be in the readout test suite?

9 October 2024: <u>https://indico.fnal.gov/event/66391/</u>

Erik, Lene Kristian, Lennart, Cristina, Jeremy, Hannah

## HGCROC board manufacturing

In production at CERN. Torsten will go to the workshop and talk with them 10 October. 4 boards in production first and then 16 more (total 20) [HGCROC board + adapter card] Planning to mail out 18 October (subject to confirmation tomorrow) - 2 at Lund (1  $\rightarrow$  Fermilab?)

- 1 UMN

- 1 UVA (or 2 to UMN and 1 at LU

- (First round)

#### Firmware stackup:

- Leverage CMS readout as much as possible in the short term to readout HGCROC board directly with Xilinx dev board

- Worry about SURF compliance next

- If we use the CMS path, we have all the blocks we need:

- Fast control

- I2C

- Standard IPs from Xilinx

- Data capture side / Link capture [needs work]

- CMS implementation complex...

- Options available

- Not super complicated to hit a reasonable data rate

- 100 Hz to kHz achievable

- Rate-dependent; we'd need to update this later

- TODO: Work out a data rate progression plan for after first QC

- Workload if board + adapter card in-hand (and no powering-type issues)  $\rightarrow$  few days for low-data rate (100Hz) firmware

What firmware blocks is UMN/ Jeremy prepared/comfortable supporting? If somebody else wants to maintain the firmware from CMS, we need permission to maintain it. If we use the CMS stackup, we need to support it ourselves.

HCAL readout electronics

timeline and work

planning, March 7

Indico indico.fnal.gov

Indico indico.fnal.gov

type instrumented with next-generation electronic

adout chain (very simplified, lines are not data lines) HOGROC HOGROC Backplane

FPGA

stable configurations and firmware across full chain

PDF Document · 171 KB

Requires: The Actual DAQ (TM) 6 + 2 HGCROC boards with fully-instrumented backplanes at SLAC Functional test stands (1 full readout system each) A Linder Stands (1 full readout system each)

HCAL readout electronics planning\_ Dis...

Design review, March 21

## ESA: All roughly the same configuration (e beam with set energy)

We'd previously identified that the backplane-less readout path for reading out a single

- HGCROC needed: ZCU development board (Xilinx FPGA)

- An adapter to connect the development board and HGCROC board (FMC site)

- HGCROC board 😎

- Firmware for the development board to read directly the HGCROC board HGCROC configurations appropriate for HGCROCv3b

| Quickly | y becomes a | software | question |

|---------|-------------|----------|----------|

|         |             |          |          |

- CMS: Microhall (similar to Rogue)

- Built-in protection layer

- Testbeam 2022: We had our own custom software

- Pflib/pftool was C++ tool for configuration/setting registers

- Not a plug-and-play solution to recycle this...

- Could have a mismatch between how these libraries were intended and what they are supposed to do now...

- pftool interface sensible; try to keep

- pflib needs to be rewritten

- Based on information passing to/from the polarfire, which doesn't work like that

- We don't want to build polarfire emulator

- ZCU also stronger processor than polarfire's was :) we can give it some work Rogue: Python-Rogue good for configuration

- Slow through Program io

- DMA required if we want to go fast

- Harder on the firmware side

- At that point, makes more sense to flop over to Stanford firmware suite

- Could get decent performance with Program io (but have to dump Python)

- TODO: Consider where we want to invest our sw dev time

#### What's a 1-time deal?

Creating an appropriate bit/byte stream for the ROCs definitely lives; probably good to develop expertise outside UMN Definitely need a new register map

Then send your register map to the ROC and start up a couple other operations

Keep core level simple as possible

- Build clear map of steps

- Setting biases

- Deciding order registers get tuned (Jeremy has some presentations lying around)

- Parameter extractions from couple of runs

Testing firmware requires building ~90% low-level software as well as the firmware itself. Other 10% PLUS next-level wrapper (take a run; take sequence of runs) should definitely be joint UMN/LU/UVA

## New HGCROC boards arrive Lund

100 H

100 H

| Ualus anne Lunu            |                                            |                                                                                                                                                                                                                                    |                                                                                                                                                                                           |

|----------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -1 week                    | HGCROC board                               | Adapter between<br>ROC and ZCU                                                                                                                                                                                                     | Includes quality control on voltages around the board;<br>checking adapter works                                                                                                          |

| ing. +1 week               |                                            |                                                                                                                                                                                                                                    |                                                                                                                                                                                           |

|                            | Firmware for the ZCU<br>to readout the ROC | Borrow from CMS,<br>need to be prepared<br>to support it                                                                                                                                                                           | Some things (eg some I2C comms) could be prepared before<br>the +2 weeks from board manufacture<br>Data/link capture most delicate and will take longer                                   |

| Hz first draft<br>+1 month | Low-level software:<br>Successor to pflib  | Control fast control<br>Set up capture blocks (phases 0.1 ns for getting data from<br>electrical link (e-link) to get bits into system; timing wrt L1A)<br>Pulling data from buffers so it can go to disk<br>Housekeeping (resets) |                                                                                                                                                                                           |

| Hz first draft<br>Evolving |                                            |                                                                                                                                                                                                                                    | nmunication with ROC<br>vare already developed<br>th data capture side (outputing byte streams or)<br>up a sequence of runs<br>e can modularize this box and split work accordingly ; map |

## Summary, 9 October 2024 meeting • <u>https://indico.fnal.gov/event/66391/</u>

Erik, Lene Kristian, Lennart, Cristina, Jeremy, Hannah

## **Backplaneless readout of HGCROC board requirements**

- HGCROC board v2 ("board")

- ROC board ↔ ZCU development board adapter card ("card")

- Firmware installed on the dev board

- · Low-level software (on a neighbouring computer) for key firmware controls/interfaces

- Wrapper-level softwares

## Board + Card availability [LU]

- 4 boards in production at CERN electronics workshop now

- Torsten will pass the workshop 10 October to get an update on the production

- 16 more boards will be produced when we approve these 4 (total 20 boards)

- Lennart will QC powering, voltage levels across the four boards before any distribution

- Could approve further production at this point, or wait for experience with readout chain

- Lennart has also designed the adapter card

- Need to actually test board + card works

- Special handling: Good idea to get a dissipative mat + use grounding wrist straps while working with the boards

## **Board + Card distribution [LU]**

- 4 board + card sets in near future

- 1 each to UMN, UVA, LU

- 1 more available

- Extra for UMN or LU?

- FNAL? Board + Card set quality-controlled before distribution

## Firmware [UMN]

- Fastest way to make firmware available: Crib off the CMS stackup

- Most firmware blocks available

- 3 main species: fast control, I2C, capture

- We cannot expect CMS to maintain our implementation or make adaptations for us.

- If somebody else (not Jeremy/UMN) wants to maintain our "fork" of CMS's firmware, we need CMS' permission • Jeremy/UMN comfortable with CMS fast control and I2C blocks. Data capture (also called link capture) needs more attention  $\rightarrow$  most delicate part and will take longer

- Capture side is readout-rate-dependent

- 100 1000 Hz reasonably achievable to implement accurately and quickly

- Readout computer attached to ZCU also has to keep up

- We agreed to start at 100 Hz

- Better to get a draft of the chain and start identifying how things work  $\rightarrow$  "Start simple, then get fancy"

- We'll need to converge with TDAQ's rates eventually

- Elected to work that timeline out separately

### Low-level software [UMN]

- Some low-level software required to test firmware

- Functions include

- Controlling fast control

- Setting up capture blocks

- Pulling data from buffers so they can go to disk

- Some housekeeping

- pflib library for 2022 testbeam not appropriate for this anymore

- Polarfire != ZCU Xilinx

- ZCU actually more powerful

- We do not want to build a Polarfire emulator

- Consider this low-level software the successor to pflib

### Wrapper softwares [LU, UVA with significant input from UMN]

- Successor to pftool

- Use pftool as a model

- Responsible for higher-level tasks requiring eg more coordination

- Setting up runs/sequences of runs

- Setting biases

- Full register map of ROCs, setting order registers get tuned

- Parameter extractions

- Key opportunity to build distributed support model and knowledge base across HCal-LDMX

### Timeline

- Setting t0 to "HGCROC boards back at LU from CERN workshop"

- [LU] Task 1 1 week: Board + adapter quality control (total time: t0 + 1 week)

- [LU] Task 2 1 week: Board + adapter distribution, waiting on shipments (total time: t0 + 2 weeks)

- [UMN] Task 3 2 weeks: Firmware preparation before board in-hand (parallel to Tasks 1, 2; total time: t0 + 2 weeks)

- [UMN] Task 4 1 month: First draft of firmware + low-level software for readout at 100 Hz distributed to LU and UVA (total time: t0 + 6 weeks)

- [UVA, LU, UMN] Task 5 evolving; to be broken down!!: Wrapper software

- [UVA, LU] Task 5.1 6 weeks: Map needed wrapper software functions into modules and begin designing implementation based on pftool (parallel to tasks 1-4; total time: t0 + 6 weeks)

- Includes breaking Task 5 down into sub-tasks and assigning time planning to those sub tasks Evolving product

- Make a plan for tracking feature requests, bug reports

- Cristina, Erik, Lene Kristian, Hannah, Gréta

- Total time estimate to viable backplaneless readout path at 100 Hz draft: t0 + 6 weeks minimum